1、输入口(Input)

输入口其实可以理解为一个对地电阻和对VDD电阻均为无穷大的端口,它的状态完全由外部电路决定。此脚不用时不能悬空,视工作情况要么接地要么到VDD。

2、输出口(Output)

输出口可由程序设定为输出高或输出低,在负载范围内,输出高时的电压约等于VDD,输出低时的电压约等于VSS。此脚不用时可悬空。

3、有内部上拉的输入口(Pull-high)

有内部上拉的输入口相当于该输入口在芯片内部接了一个150K左右的电阻到VDD。因此,与普通输入口相比,有内部上拉的输入口在外围悬空的情况下测量的电压近似于VDD(不用时可悬空),而普通输入口在外围悬空的情况下测量的电压是不确定的,在VSS~VDD之间变化,实际运用时是不能悬空的。

4、开漏输出(Open-dnain)

开漏输出的输出口特性如下:输出低时对VSS阻抗极低,在负载范围内近似于VSS;输出高时对VSS和VDD阻抗视为无穷大,输出电压取决于外部电路提供的电压(最大为芯片极限存受电压)。

5、I/O口

顾名思义同一脚即是输入口又是输出口,在不同的时候是不同的状态,视工作情况考虑外部电路;此脚有输入状态,所以不用时不能悬空,也不能直接接地或接VDD,需通过47K以上的电阻上拉到VDD或下拉到地。

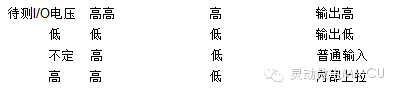

6、如何准确判断输入/输出状态

下面通过一个电阻就可以准确判断出I/O的输入/输出状态。

请参考下表:

7、I/O的内部保护

I/O一般都有内部保护电路,均采用二极管钳位保护,保证I/O的电压不超过VDD+0.7V且不低于VSS-0.7V,确保I/O不因外部一定的电压而受到损伤。

8、应用注意事项

所有输入口均不能悬空(内部上拉的输入口除外),必须通过外部电路接上稳定的高或低电位,否则会导致MCU的耗电剧增或工作状态的变化。

硬件电路设计中应确保各脚的电压不超过VDD且不低于VSS,否则将不仅会使MCU电流增大且又极易损坏芯片。 芯片外围电路设计时必须确保芯片的供电电压在其允许范围之内。

9、关于单片机高、低电位的判断 单片机输入口读取高、低电平的判断与芯片供电的VDD有直接关系,VDD不同,判断高、低的临界电压值也不一样。根据IC资料,≥2/3VDD的电压MCU判断为高,而≤1/3VDD的电压值MCU判断为低,中间有一定的模糊区,而实际应用的经验告诉我们,单片机读到高比较容易而不容易读到低,一般0.7V的电压才可以准确读到低。

文章来源:互联网