BRAM

Xilinx Vitis 2020.1修改工程占用的BRAM内存大小的方法

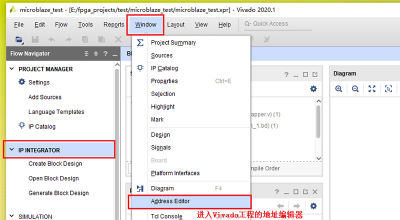

修改了代码后编译工程,有时会因为BRAM空间不足而编译失败,出现下面的错误提示,这时,需要回到Vivado工程里面,在Block Design中将分配的BRAM空间大小改大。具体方法如下。

XILINX BMG (Block Memory Generator)

XILINX 系列的 FPGA ,如果想要做一个 RAM,有两种方式:

1、使用逻辑资源组成分布式 RAM,即 Distributed RAM

2、使用 XILINX 专用的 Block RAM,即 BRAM

URAM和BRAM有什么区别

无论是7系列FPGA、UltraScale还是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我们所说的URAM。BRAM和URAM都是重要的片上存储资源,但两者还是有些显著的区别。

Block RAM与Distributed RAM

Block RAM与Distributed RAM,简称为BRAM与DRAM, 要搞清楚两者的区别首先要了解FPGA的结构: FPGA=CLB + IOB+Block RAM CLB。一个CLB中包含2个Slice、8位寄存器、多路选择器、进位链等。

ZynqNet解析(七)实现于BRAM上的Cache

背景:我们需要仿照ZynqNet的模式构造卷积的IPcore用于FPGA的优化。

目的:搞懂zynqNet的cache的实现。

分页

- 前一页

- 页面 2