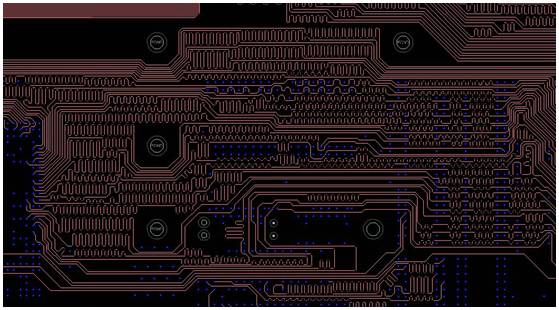

PCB设计

根据经验总结的PCB设计完成后需要检查的内容

1. 检查高频、 高速、 时钟及其他脆弱信号线, 是否回路面积最小、 是否远离干扰源、 是否有多余的过孔和绕线、是否有垮地层分割区

2. 检查晶体、 变压器、 光藕、 电源模块下面是否有信号线穿过, 应尽量避免在其下穿线,特别是晶体下面应尽量铺设接地的铜皮。

3. 检查定位孔、定位件是否与结构图一致, ICT定位孔、 SMT定位光标是否加上并符合工艺要求。

4. 检查器件的序号是否按从左至右的原则归宿无误的摆放规则,并且无丝印覆盖焊盘;检查丝印的版本号是否符合版本升级规范,并标识出。

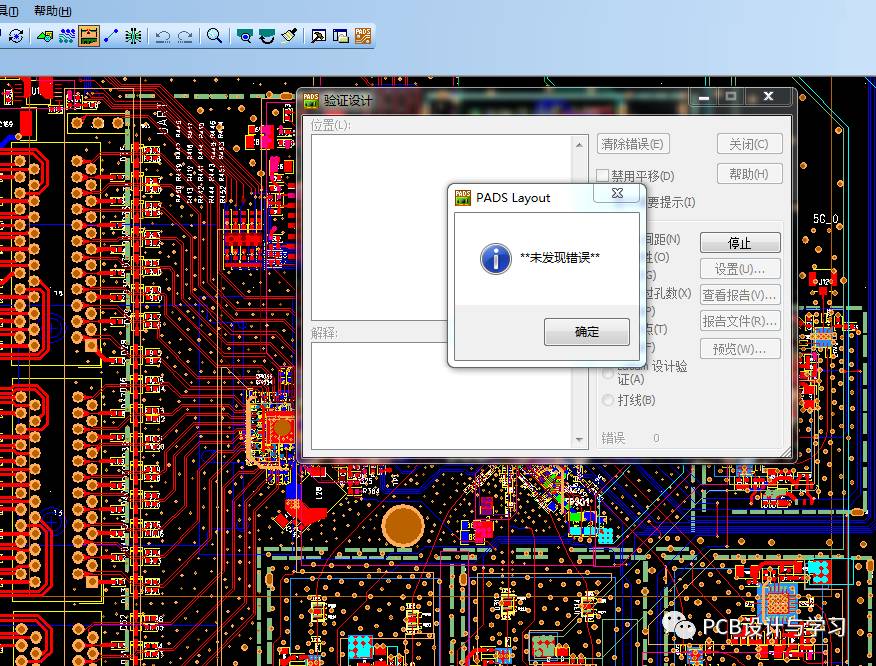

5. 报告布线完成情况是否百分之百;是否有线头;是否有孤立的铜皮。

6. 检查电源、地的分割正确;单点共地已作处理;

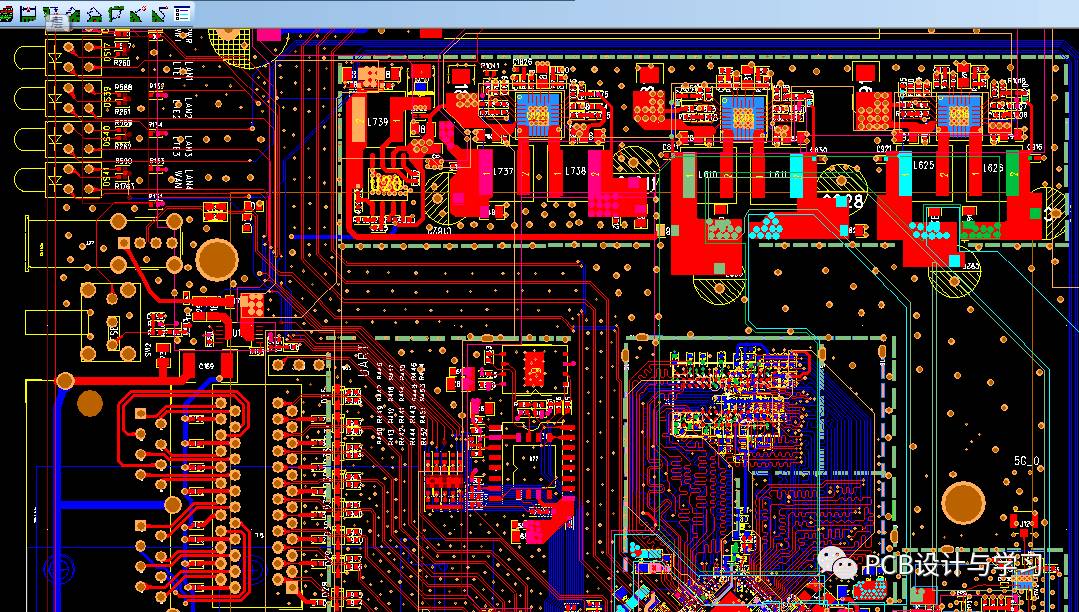

PCB设计十大误区-绕不完的等长(五)

作者:吴均 一博科技高速先生团队队长

1、串行总线来了

绕线话题从开篇到结尾,花了好几个月哈,老是出差,没有时间静下来写东西。不过或许出差也只是借口,而是因为时序绕线这个话题实在是有点难写好吧。不管怎么说,挖下的坑是一定要埋上的,今天就是绕不完的等长的最后一篇,串行总线来了。

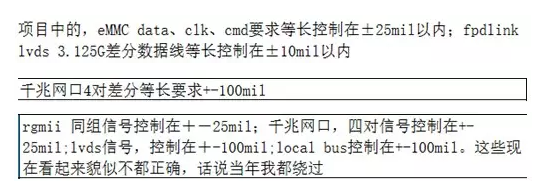

上一篇文章发出来之后,不少网友回复说,DDR3的同组数据并不需要做到5mil等长这么严格呀。看到这样的回复,高速先生们都是热泪盈眶:“同志,见到你真好……”。说实话,写这个系列文章还是有点私心的,希望以后不会再收到客户提出的+/-1mil,+/-0.5mil等长这样的要求,我们已经是很满足了。+/-5mil或者+/-10mil,这已经不是个事了,咬咬牙,加点班,这个等长我们就忍了。

到了串行总线,貌似速率更高了,大家对等长的要求也更严格了。那么串行总线到底是什么鬼?

PCB设计十大误区-绕不完的等长(二)

作者:吴均 一博科技高速先生团队队长

Part 1、关于等长与等时

绕线系列的第一篇文章发完之后,就开始准备美国研讨会,然后就是长达一个月的出差。终于有时间继续这个话题了,先来看看之前大家的回复,我隐去了回复者的名字,只保留了答案:

游戏开始,大家直接回复高速先生本微信号,列举下自己做过的,或者认可的等长设计要求,之前的部分答复如下:

…… ……

之前也提过,现在流行重要的事情说三遍:

1、等长从来都不是目的,系统要求的是等时……

2、除了差分对内的等时是为了相位之外,绝大多数的等时都是为了时序!

3、为了时序而绕线,就一定要搞通时序关系,看懂时序图

每次看到时序图的时候,都会眼前一黑有没有?

PCB设计十大误区-绕不完的等长(一)

作者:吴均 一博科技高速先生团队队长

1、关于等长

第一次听到“绕等长工程师”这个称号的时候,我和我的小伙伴们都惊呆了。每次在研讨会提起这个名词,很多人也都是会心一笑。

不知道从什么时候起,绕等长成了一种时尚,也成了PCB设计工程师心中挥不去的痛。需要等长设计的总线越来越多,等长的规则越来越严格。5mil已经不能满足大家的目标了,精益求精的工程师们开始挑战1mil,0.5mil……还听过100%等长,没有误差的要求。

为什么我们这么喜欢等长?打开PCB设计文件,如果没有看到精心设计的等长线,大家心中第一反应应该是鄙视,居然连等长都没做。也有过在赛格买主板或者显卡的经验,拿起板子先看看电容的设计,然后再看看绕线,如果没有绕线或者绕线设计不美观,直接就Pass换另一个牌子。或许在我们的心中,等长做的好,是优秀PCB设计的一个体现。

分页

- 页面 1

- 下一页