PCB设计十大误区-绕不完的等长(二)

<strong><font color="#004a85">作者:吴均 一博科技高速先生团队队长</font> </strong>

<strong>Part 1、关于等长与等时</strong>

绕线系列的第一篇文章发完之后,就开始准备美国研讨会,然后就是长达一个月的出差。终于有时间继续这个话题了,先来看看之前大家的回复,我隐去了回复者的名字,只保留了答案:

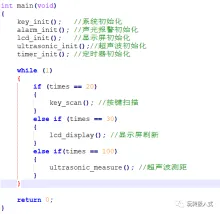

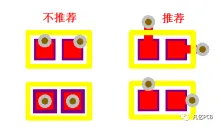

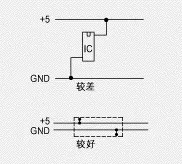

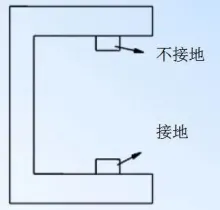

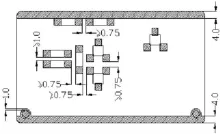

游戏开始,大家直接回复高速先生本微信号,列举下自己做过的,或者认可的等长设计要求,之前的部分答复如下:

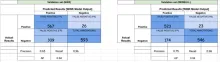

<center><img src="http://mouser.eetrend.com/files/2021-01/博客/100061329-120788-1.png" alt=“"></center>

…… ……

之前也提过,现在流行重要的事情说三遍: